Lattice Semiconductor Nexus Platform

Lattice Semiconductor Nexus Platform combines Lattice's long-standing low-power FPGA expertise with leading 28nm fully depleted silicon-on-insulator (FD-SOI) semiconductor manufacturing technology. With this platform, Lattice enables the rapid development of multiple device families that deliver low power, high performance, high reliability, and a small form factor.

Three levels of innovation are provided by the Lattice Nexus FPGA Platform:

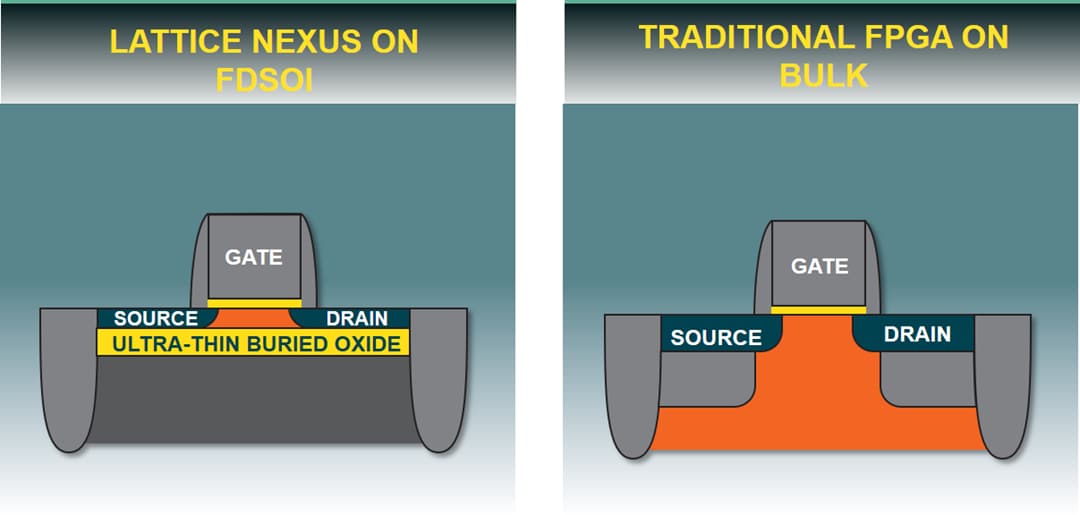

- Circuit: 75% lower power, 100x lower soft error rate as compared with the bulk process

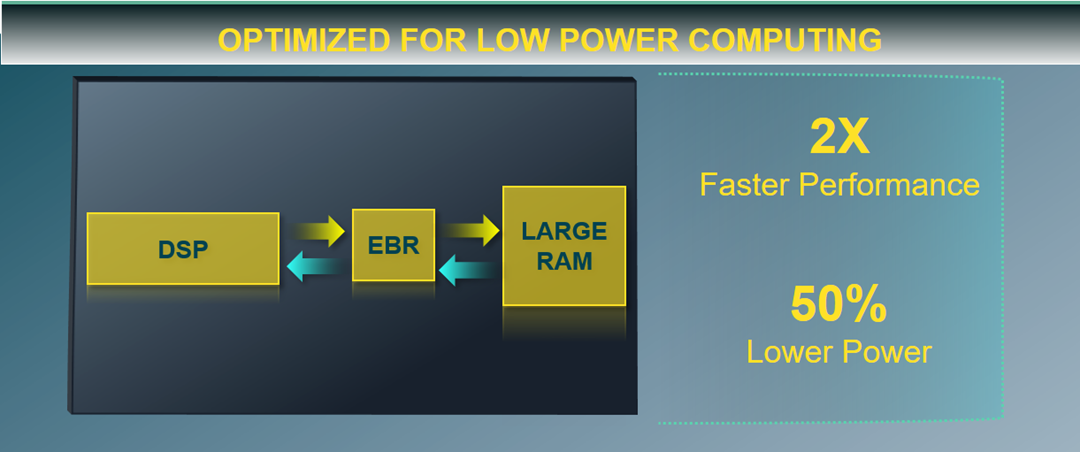

- Architecture: Embedded large RAM blocks optimize the implementation of common AI algorithms

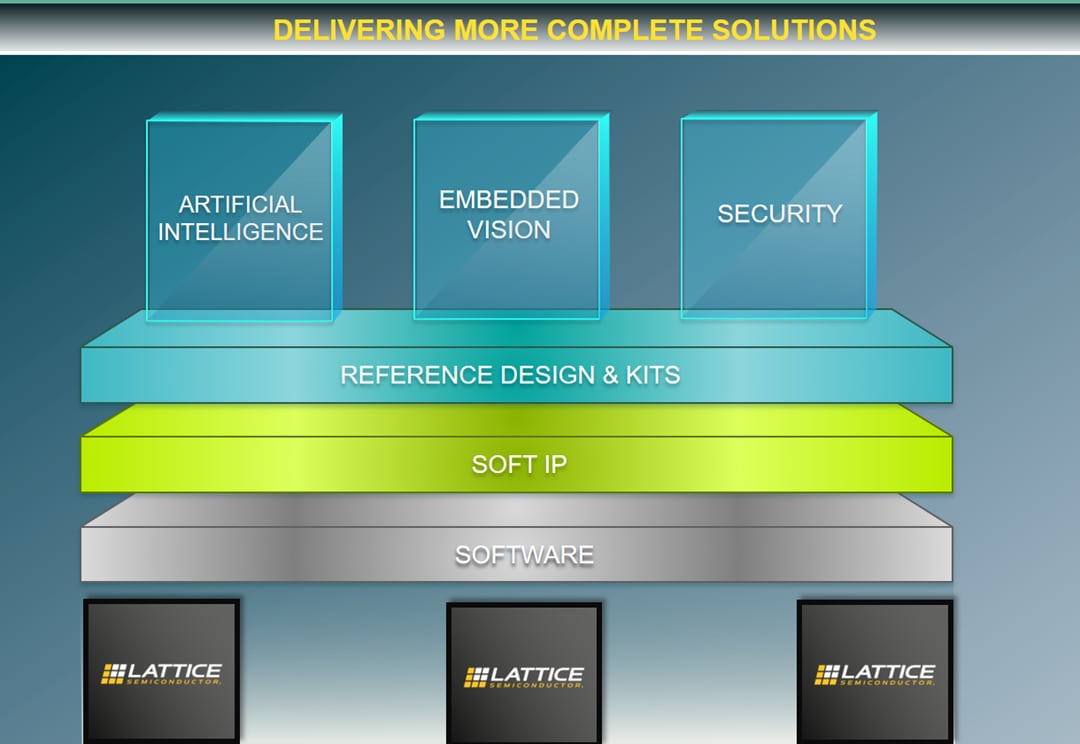

- Solutions: Delivering more complete solutions with IP, reference designs, and software stacks

Videos

Circuit

- Programmable back bias enabled by the insulated gate of FD-SOI technology delivers performance/power optimization

- Critical area (orange) size reduction provides 100x SER reliability improvement

- FD-SOI leverages bulk CMOS process and has fewer processing steps

Architecture

- Optimized for Edge computing with embedded large RAM

- Improves performance by avoiding off-chip memory access

- Eliminates power consumption associated with accessing external memory

Solutions

- Solutions focus on AI, embedded vision, and security

- Reference design, kits, soft IP, and software accelerate product development

- Complete end-to-end solution offerings enable faster time-to-market

Published: 2020-03-06

| Updated: 2025-03-24